1Īóā╚┤µ╗∙ĄA

ĪĪĪĪRDRAM(Rambus)ĪóDDR SDRAM╔§ų┴╩ŪEDO RAMį┌▒Š┘|╔Žųv╩Ūę╗śėĄ─ĪŻRDRAMĪóDDR RAMĪóSDRAMĪóEDO RAMČ╝ī┘ė┌DRAM(Dynamic RAM)Ż¼╝┤äėæBā╚┤µĪŻ╦∙ėąĄ─DRAM╗∙▒Šå╬╬╗Č╝╩Ūė╔ę╗éĆŠ¦¾w╣▄║═ę╗éĆļŖ╚▌Ų„ĮM│╔ĪŻ

ĪĪĪĪ╔ŽłDų╗╩ŪDRAMę╗éĆ╗∙▒Šå╬╬╗Ą─ĮYśŗ╩ŠęŌłDŻ║ļŖ╚▌Ų„Ą─ĀŅæBøQČ©┴╦▀@éĆDRAMå╬╬╗Ą─▀ē▌ŗĀŅæB╩Ū1▀Ć╩Ū0Ż¼ę╗éĆļŖ╚▌Ų„┐╔ęį┤µā”ę╗Č©┴┐Ą─ļŖūė╗“š▀╩ŪļŖ║╔ĪŻę╗éĆ│õļŖĄ─ļŖ╚▌Ų„į┌öĄūųļŖūėųą▒╗šJ×ķ╩Ū▀ē▌ŗ╔ŽĄ─1Ż¼Č°Ī░┐šĪ▒Ą─ļŖ╚▌Ų„ät╩Ū0ĪŻļŖ╚▌Ų„▓╗─▄│ųŠ├Ą─▒Ż│ųā”┤µĄ─ļŖ║╔Ż¼╦∙ęįā╚┤µąĶę¬▓╗öÓČ©Ģr╦óą┬Ż¼▓┼─▄▒Ż│ųĢ║┤µĄ─öĄō■ĪŻļŖ╚▌Ų„┐╔ęįė╔ļŖ┴„üĒ│õļŖĪ¬«ö╚╗▀@éĆļŖ┴„╩Ūėąę╗Č©Ž▐ųŲĄ─Ż¼Ę±ätĢ■░čļŖ╚▌ō¶┤®ĪŻ═¼ĢrļŖ╚▌Ą─│õĘ┼ļŖąĶę¬ę╗Č©Ą─ĢrķgŻ¼ļm╚╗ī”ė┌ā╚┤µ╗∙▒Šå╬╬╗ųąĄ─ļŖ╚▌▀@éĆĢrķg║▄Č╠Ż¼ų╗ėą┤¾╝s0.2-0.18╬ó├ļŻ¼Ą½╩Ū▀@éĆŲ┌ķgā╚┤µ╩Ū▓╗─▄ł╠ąą┤µ╚Ī▓┘ū„Ą─ĪŻ

ĪĪĪĪā╚┤µų┴╔┘ę¬├┐64ms╦óą┬ę╗┤╬Ż¼▀@ę▓Š═ęŌ╬Čų°ā╚┤µėą1ŻźĄ─Ģrķgę¬ė├üĒ╦óą┬ĪŻā╚┤µūįäė╦óą┬Ą─ĻPµIį┌ė┌«öī”ā╚┤µå╬į¬▀Mąąūx╚Ī▓┘ū„Ģr▒Ż│ųā╚┤µĄ─ā╚╚▌▓╗ūāĪ¬╦∙ęįDRAMå╬į¬├┐┤╬ūx╚Ī▓┘ū„ų«║¾Č╝ę¬▀Mąą╦óą┬Ż║ł╠ąąę╗┤╬╗žīæ▓┘ū„Ż¼ę“×ķūx╚Ī▓┘ū„ę▓Ģ■ŲŲē─ā╚┤µųąĄ─ļŖ║╔Ż¼ę▓Š═╩Ūšfī”ė┌ā╚┤µųą┤µā”Ą─öĄō■╩ŪŠ▀ėąŲŲē─ąįĄ─ĪŻ╦∙ęįā╚┤µ▓╗Ą½ę¬├┐64ms╦óą┬ę╗┤╬Ż¼├┐┤╬ūx▓┘ū„ų«║¾ę▓ę¬╦óą┬ę╗┤╬ĪŻ▀@śėŠ═į÷╝ė┴╦┤µ╚Ī▓┘ū„Ą─ų▄Ų┌Ż¼«ö╚╗ØōĘ³Ų┌ę▓Š═įĮķLĪŻ

ĪĪĪĪSRAMŻ¼ņoæB(Static)RAM▓╗┤µį┌╦óą┬Ą─å¢Ņ}Ż¼ę╗éĆSRAM╗∙▒Šå╬į¬░³└©4éĆŠ¦¾w╣▄║═2éĆļŖūĶĪŻ╦³▓╗╩Ū═©▀^└¹ė├ļŖ╚▌│õĘ┼ļŖĄ─╠žąįüĒ┤µā”öĄō■Ż¼Č°╩Ū└¹ė├įOų├Š¦¾w╣▄Ą─ĀŅæBüĒøQČ©▀ē▌ŗĀŅæBĪ¬═¼CPUųąĄ─▀ē▌ŗĀŅæBę╗śėĪŻūx╚Ī▓┘ū„ī”ė┌SRAM▓╗╩ŪŲŲē─ąįĄ─Ż¼╦∙ęįSRAM▓╗┤µį┌╦óą┬Ą─å¢Ņ}ĪŻ

2ĪóSDRAMĄ─ĮYśŗ║═╣”─▄

ĪĪĪĪā╚┤µūŅ╗∙▒ŠĄ─å╬╬╗╩Ūā╚┤µĪ░╝Ü░¹Ī▒Ī¬ę▓Š═╩Ū╬ęéāŪ░├µš╣╩ŠĮo┤¾╝ęDRAM╗∙▒Šå╬į¬╩ŠęŌłD╦∙╩ŠĄ─▓┐ĘųŻ¼ī”▀@éĆ▓┐Ęų═©ĘQ×ķDRAM╗∙▒Šå╬į¬ĪŻ├┐éĆDRAM╗∙▒Šå╬į¬┤·▒Ēę╗éĆĪ░╬╗Ī▒Ī¬Bit(ę▓Š═╩Ūę╗éĆ▒╚╠ž)Ż¼▓óŪęėąę╗éĆė╔┴ąĄžųĘ║═ąąĄžųĘČ©┴xĄ─╬©ę╗ĄžųĘĪŻ8éĆ▒╚╠žĮM│╔ę╗éĆūų╣ØŻ¼╦³┐╔┤·▒Ē256ĘNĮM║Ž(╝┤2Ą─░╦┤╬āń)Ż¼ūų╣Ø╩Ūā╚┤µųąūŅąĪĄ─┐╔īżųĘå╬į¬ĪŻ

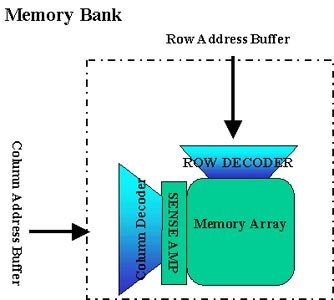

ĪĪĪĪ║▄ČÓDRAM╗∙▒Šå╬į¬▀BĮėĄĮ═¼ę╗éĆ┴ąŠĆ(Row line)║══¼ę╗éĆąąŠĆ(Column line)Ż¼ĮM│╔┴╦ę╗éĆŠžĻćĮYśŗŻ¼▀@éĆŠžĻćĮYśŗŠ═╩Ūę╗éĆBankĪŻ┤¾▓┐ĘųĄ─SDRAMąŠŲ¼ė╔4éĆBankĮM│╔Ż¼Č°SDRAM DIMM(Dual Inline Memory Moduleļp┴ąų▒▓Õ╩Į)┐╔─▄ė╔8╗“š▀16éĆąŠŲ¼ĮM│╔ĪŻSDRAM DIMMėą14ŚlĄžųĘŠĆ║═64bitöĄō■ŠĆĪŻ

ĪĪĪĪ├┐ę╗éĆā╚┤µbankČ╝ėąę╗éĆé„ĖąĘ┼┤¾Ų„(sense ampplifier),ė├üĒĘ┼┤¾Å─╗∙▒Šå╬į¬ūx│÷(╗“š▀īæ╚ļ)ā╚╚▌ĢrļŖ║╔ĪŻé„ĖąĘ┼┤¾Ų„Ė∙ō■Å─ąŠŲ¼ĮM░l╦═üĒĄ─ąąĄžųĘūx│÷ŽÓæ¬Ą─öĄō■Ż¼▀@éĆūx│÷▀^│╠ąĶę¬ę╗Č©Ą─Ģrķg▀@Š═╩ŪRASĄĮCASĄ─čė▀tŻ¼║åĘQTRCDĪŻ▓╗═¼┘|┴┐Ą─SDRAMĄ─TRCDąĶę¬2╗“š▀3éĆų▄Ų┌ĪŻ¼Fį┌ęčĮøėą┴╦š²┤_Ą─ąąĄžųĘŻ¼▓╗▀^▀Ć▓╗ų¬Ą└┤_ŪąĄ─ĄĮ─ŪéĆ╗∙▒Šå╬į¬╚ź½@Ą├ą┼ŽóĪŻCASčė▀tĢrķgŠ═╩Ūā╚┤µė├ė┌╚ĪĄ├š²┤_Ą─┴ąĄžųĘ╦∙ąĶꬥ─ĢrķgĪŻ

ĪĪĪĪūóŻ║Latency(čė▀t)╩Ūę╗ĘNĄ╚┤²Ą─ĢrķgŻ¼▀@┼cā╚┤µąŠŲ¼▒Š╔ĒėąĻPĪŻ─ŪéĆC╗“CASųĖĄ─╩ŪColumn Address Strobe(ąąĄžųĘ┐žųŲŲ„)ĪŻ╬ęéā▓╗Ę┴īóā╚┤µŽļ│╔ā”┤µöĄō■Ą─öĄĮMĪó╗“╩Ū▒ĒĖ±ĪŻ×ķ┴╦ę¬┤_Č©├┐éĆöĄō■Ą─╬╗ų├Ż¼╬ęéāĢ■īó▀@ą®╬╗ų├ęįąą┼c┴ąĄ─ĘĮ╩ĮüĒŠÄ╠¢ĪŻ╚ń┤╦ę╗üĒŻ¼š²╚ń╦∙ŽļęŖĄ─Ż¼│²┴╦CAS(ąąĄžųĘ┐žųŲŲ„)ęį═ŌŻ¼▀ĆėąRAS(┴ąĄžųĘ┐žųŲŲ„)ĪŻ

ĪĪĪĪā╚┤µ╗∙▒Šå╬į¬Š═░čą┼╠¢░l╦═ĄĮDIMMĄ─▌ö│÷ŠÅ┤µŻ¼▀@śėąŠŲ¼ĮMŠ═┐╔ęįūx╚Ī╦³éā┴╦ĪŻ¼Fį┌╬ęéāėą┴╦Ū░8éĆūų╣ØĄ─ā╚╚▌Ż¼ęį╝░į┌é„ĖąĘ┼┤¾Ų„ųąėą┴╦š²┤_Ą─ąąĄžųĘŻ¼Ą╚ĄĮŽ┬├µĄ─24éĆūų╣ØĄ─▀^│╠Š═║åå╬┴╦ĪŻ▀@ĢrŠ═ė╔ā╚▓┐ėŗöĄŲ„žōž¤░čŽ┬ę╗éĆ┴ąĄžųĘĄ─ā╚┤µ╗∙▒Šå╬į¬Ą─ā╚╚▌░l╦═ĄĮDIMMĄ─▌ö│÷ŠÅ┤µ«öųąĪŻ▀@śė├┐éĆĢrńŖų▄Ų┌Č╝ėą8éĆūų╣Øé„╦═ĄĮ▌ö│÷ŠÅ┤µųąŻ¼▀@ĘN─Ż╩ĮŠ═Įąū÷Ī░═╗░l─Ż╩ĮĪ▒ĪŻ

ĪĪĪĪų„ā╚┤µĄ─čė▀tĢrķg(ę▓Š═╩Ū╦∙ų^Ą─ØōĘ³Ų┌Ż¼Å─FSBĄĮDRAM)Ą╚ė┌Ž┬┴ąĢrķgĄ─ŠC║ŽŻ║FSB═¼ų„░ÕąŠŲ¼ĮMų«ķgĄ─čė▀tĢrķg(+/- 1éĆĢrńŖų▄Ų┌)Ż¼ąŠŲ¼ĮM═¼DRAMų«ķgĄ─čė▀tĢrķg(+/- 1éĆĢrńŖų▄Ų┌)Ż¼RASĄĮCASčė▀tĢrķgŻ║RCD(2-3 éĆĢrńŖų▄Ų┌,ė├ė┌øQČ©š²┤_Ą─ąąĄžųĘ)Ż¼CASčė▀tĢrķg (2-3 ĢrńŖų▄Ų┌,ė├ė┌øQČ©š²┤_Ą─┴ąĄžųĘ)Ż¼┴Ē═Ō▀ĆąĶę¬1éĆĢrńŖų▄Ų┌üĒé„╦═öĄō■Ż¼öĄō■Å─DRAM▌ö│÷ŠÅ┤µ═©▀^ąŠŲ¼ĮMĄĮCPUĄ─čė▀tĢrķg(+/- 2éĆĢrńŖų▄Ų┌)ĪŻ

ĪĪĪĪ┐╔ęį┐┤│÷Ż¼ę╗éĆšµš²Ą─PC100Ą─SDRAM(CASŻĮ2)Ą─ā╚┤µ╚ĪĄ├ūŅŪ░░╦éĆūų╣ØĄ─Ģrķg╩Ū9éĆĢrńŖų▄Ų┌Ż¼Č°┴Ē═Ō24éĆūų╣Øų╗╩ŪąĶę¬3éĆĢrńŖų▄Ų┌Ż¼▀@śėPC100Ą─SDRAM╚ĪĄ├32éĆūų╣ØĄ─öĄō■ų╗╩ŪąĶę¬12éĆĢrńŖų▄Ų┌ĪŻī”ė┌═¼śėĄ─ŪķørŻ¼ę▓Š═╩Ū«öČ■╝ēŠÅ┤µ╬┤├³ųąĄ─Ģr║“Ż¼CPUÅ─ā╚┤µ╚ĪĄ├öĄō■╦∙ąĶꬥ─čė▀tĢrķgąĶę¬ė├╚ńŽ┬ĘĮĘ©ėŗ╦ŃŻ║CPU▒ČŅlĪ┴ā╚┤µčė▀tĢrķgŻĮCPUčė▀tĢrķgĪŻ╚ń╣¹500MHZ(5Ī┴100MHz)Ą─CPUąĶę¬5Ī┴9éĆčė▀tų▄Ų┌ĪŻę▓Š═╩Ūšf╚ń╣¹Č■╝ēŠÅ┤µø]ėą├³ųąŻ¼CPUąĶę¬45éĆĢrńŖųąŲ┌▓┼─▄Ą├ĄĮą┬Ą─öĄō■ĪŻ

ĪĪĪĪŠ┐Š╣╩Ū╩▓├┤øQČ©DRAM╦┘Č╚Ż┐SDRAM╩ŪČÓbankĮYśŗŻ¼ąŠŲ¼ĮM┐╔ęį▒Ż│ųę╗▓┐Ęųį°ĮøįLå¢▀^Ą─BankĄ─ąąĄžųĘŻ¼ę▓Š═╩Ūšf▒Ż│ųę╗▓┐ĘųęčĮø▒╗┤“ķ_Ą─Ī░Ēō├µĪ▒ĪŻ╚ń╣¹ąĶę¬įLå¢Ą─öĄō■į┌═¼ę╗┴ąųąŻ¼─Ū├┤ąŠŲ¼ĮM▓╗ąĶꬥ╚┤²é„ĖąŲ„▀MąąūāōQĪ¬▀@ĘNŪķørŠ═Įąū÷Ēō├µ├³ųąĪŻ

ĪĪĪĪ▀@ĢrRASĄĮCASčė▀tĢrķgŠ═╩Ū0éĆĢrńŖų▄Ų┌Ż¼ų╗ąĶę¬Įø▀^CASčė▀tŠ═─▄į┌ā╚┤µŠÅø_š{╚ļš²┤_öĄō■ĪŻ╦∙ęįŻ¼Ēō├µ├³ųąŠ═ęŌ╬Čų°╬ęéāų╗ąĶꬥ╚┤²┴ąĄžųĘĄ─┤_┴óŻ¼Š═─▄Ą├ĄĮąĶꬥ─öĄō■┴╦ĪŻ▓╗▀^ėąĄ─ŪķørŽ┬Ż¼ąŠŲ¼ĮMšłŪ¾Ą─ā╚┤µĒō├µ▓╗╩Ū╠Äė┌┤“ķ_Ą─ĀŅæBŻ¼▀@Š═Įąū÷Ēō├µ╩¦ą¦ĪŻį┌▀@ĘNŪķørŽ┬Ż¼RASĄĮCASčė▀tĢrķgīó╩Ū2╗“š▀3ĢrńŖų▄Ų┌(Ė∙ō■ā╚┤µĄ─ŲĘ┘|▓╗═¼Č°▓╗═¼)ĪŻ▀@ĘNŪķørŠ═╩ŪŪ░├µ╬ęéāėæšō▀^Ą─Ūķą╬ĪŻ

ĪĪĪĪ╚ń╣¹ąŠŲ¼ĮMęčĮø▒Ż│ų┴╦─│ę╗éĆBankĄ──│ę╗éĆąąĄžųĘŻ¼ę▓Š═╩Ūį┌─│ę╗éĆbankęčĮø┤“ķ_┴╦ę╗éĆĒō├µŻ¼Č°šłŪ¾Ą─öĄō■╩Ū╬╗ė┌═¼ę╗éĆbankĄ─▓╗═¼ąąĄžųĘĄ─öĄō■Ż¼▀@ĘNŪķør╩ŪūŅįŃĖŌĄ─ĪŻ▀@śėŠ═ęŌ╬Čų°é„ĖąĘ┼┤¾Ų„ąĶę¬╩ūŽ╚╗žīæ┼fĄ─ąąĄžųĘŻ¼╚╗║¾į┘▐DōQą┬Ą─ąąĄžųĘĪŻ╗žīæ┼fĄ─ąąĄžųĘ╦∙š╝ė├Ą─ĢrķgĮąū÷Ī░ŅA▐DōQĢrķgĪ▒(Precharge time)Ż¼«öė÷ĄĮ▀@ĘNŪķørĢrŻ¼╩ŪūŅē─Ą─ŪķørĪŻ

ĪĪĪĪ▀@├┤šf┐╔─▄ėą³cÅ═ļsŻ¼╬ęéāōQéĆ║åå╬³cĄ─šfĘ©Ż║×ķ┴╦ę¬ūx│÷╗“īæ╚ļ─│╣PöĄō■Ż¼ā╚┤µ┐žųŲąŠŲ¼Ģ■Ž╚é„╦═┴ąĄ─ĄžųĘŻ¼ĮėŽ┬üĒRASą┼╠¢Š═Ģ■▒╗╝ż╗ŅĪŻ╚╗Č°Ż¼į┌┤µ╚ĪąąĄ─öĄō■Ū░Ż¼▀ĆąĶę¬ÄūéĆł╠ąąų▄Ų┌▓┼ąąŻ¼▀@Š═╩Ū╦∙ų^Ą─RAS-to-CASčė▀tĢrķgĪŻ═¼śėĄ─Ż¼į┌CASą┼╠¢▒╗ł╠ąą║¾Ż¼ę▓═¼śėąĶę¬ÄūéĆų▄Ų┌ĪŻ╩╣ė├ś╦ £╩PC133Ą─SDRAM┤¾╝s╩Ū2ĄĮ3éĆų▄Ų┌Ż╗Č°DDR RAMät╩Ū4ĄĮ5éĆų▄Ų┌ĪŻį┌DDRųąŻ¼šµš²Ą─CASčė▀tĢrķgät╩Ū2ĄĮ2.5éĆł╠ąąų▄Ų┌ĪŻ

ĪĪĪĪRAS-to-CASĄ─ĢrķgätęĢ╝╝ągČ°Č©Ż¼┤¾╝s╩Ū5ĄĮ7éĆų▄Ų┌Ż¼▀@ę▓╩Ūčė▀tĄ─╗∙▒Šę“╦žĪŻ─Ńę▓┐╔ęįšf┼cCL2.5(DDR)╗“CL3(SDRAM)▒╚ŲüĒŻ¼CL2ā╚┤µĖ³Š▀ā×ä▌ĪŻ└Ēšō╔ŽŻ¼▀@╩Ū╩┬īŹŻ¼Ą½▀ĆėąŲõ╦³Ą─ę“╦žĢ■ė░Ēæ▀@éĆöĄō■Ż¼└²╚ńŻ¼ą┬ę╗┤·╠Ä└ĒŲ„Ą─Ė▀╦┘ŠÅ┤µ▌^ėąą¦┬╩Ż¼▀@▒Ē╩Š╠Ä└ĒŲ„▒╚▌^╔┘ų▒ĮėÅ─ā╚┤µūx╚ĪöĄō■ĪŻį┘š▀Ż¼┴ąĄ─öĄō■Ģ■▒╚▌^│Ż▒╗┤µ╚ĪŻ¼╦∙ęįRAS-to-CASĄ─░l╔·ÖC┬╩ę▓┤¾Ż¼ūx╚ĪĄ─Ģrķgę▓Ģ■ūāČÓĪŻūŅ║¾Ż¼ėąĢrĢ■░l╔·═¼Ģrūx╚Ī┤¾┴┐öĄō■Ą─Ūķą╬Ż¼į┌▀@ĘNŪķą╬Ž┬Ż¼ŽÓÓÅĄ─ā╚┤µöĄō■Ģ■ę╗┤╬▒╗ūx╚Ī│÷üĒŻ¼CASčė▀tĢrķgų╗Ģ■░l╔·ę╗┤╬ĪŻ

╚²Īóā╚┤µĄ─░lš╣Üv│╠

ĪĪĪĪŲ│§Ż¼ļŖ─X╦∙╩╣ė├Ą─ā╚┤µ╩Ūę╗ēKēKĄ─ICŻ¼╬ęéā▒žĒÜ░č╦³éā║ĖĮėĄĮų„ÖC░Õ╔Ž▓┼─▄š²│Ż╩╣ė├Ż¼ę╗Ą®─│ę╗ēKā╚┤µICē─┴╦Ż¼▒žĒÜ║ĖŽ┬üĒ▓┼─▄Ė³ōQŻ¼▀@īŹį┌╩Ū╠½┘Mä┼┴╦ĪŻ║¾üĒŻ¼ļŖ─XįOėŗ╚╦åT░l├„┴╦─ŻēK╗»Ą─Ślčbā╚┤µŻ¼├┐ę╗Śl╔Ž╝»│╔┴╦ČÓēKā╚┤µICŻ¼ŽÓæ¬ĄžŻ¼į┌ų„░Õ╔ŽįOėŗ┴╦ā╚┤µ▓Õ▓█Ż¼▀@śėŻ¼ā╚┤µŚlŠ═┐╔ļSęŌ▓ąČ┴╦Ż¼Å─┤╦Ż¼ā╚┤µĄ─ŠSą▐║═öU│õČ╝ūāĄ├ĘŪ│ŻĘĮ▒ŃĪŻ

ĪĪĪĪį┌80286ų„░ÕĢr┤·Ą─Ģr║“Ż¼ā╚┤µŚl×ķ30pinĪó256kbŻ¼Č°Ūę▒žĒÜ╩Ūė╔9Ų¼Ņw┴Ż(Ųõųą8Ų¼×ķöĄō■╬╗Ż¼1Ų¼×ķąŻ“×╬╗)ĮM│╔ę╗éĆbank(ĮM)ĪŻĄĮ┴╦486Ģr┤·ā╚┤µų„ę¬╩Ū30PIN SIMM FPM║═72PIN SIMM FPMČ■Ęų╠ņŽ┬ĪŻFPM RAMę▓ĘQĪ░┐ņĒō─Ż╩Įā╚┤µĪ▒Ż¼╩Ūė├į┌486╝░▒╝“v╝ēėŗ╦ŃÖCĄ─Ųš═©ā╚┤µŻ¼×ķ72ŠĆŻ¼5VļŖē║Ż¼Ä¦īÆ×ķ32bitŻ¼╦┘Č╚╗∙▒ŠČ╝į┌60nsęį╔ŽĪŻ

ĪĪĪĪEDO(EXTENDED DATA OUT)RAMę▓ĘQĪ░öUš╣öĄō■▌ö│÷ā╚┤µĪ▒┼cFPM RAMėą╗∙▒ŠŽÓ═¼Ą─æ¬ė├ĘČć·Ż¼ėą72ŠĆ║═168ŠĆų«ĘųŻ¼5VļŖē║Ż¼Ä¦īÆ32bitŻ¼╦┘Č╚╗∙▒ŠČ╝╩Ū40nsęį╔ŽĪŻė╔ė┌▒╝“v╝░Ųõęį╔Ž╝ēäeĄ─CPUöĄō■┐éŠĆīÆČ╚Č╝╩Ū64bit╔§ų┴Ė³Ė▀Ż¼╦∙ęįEDO RAM┼cFPM RAMČ╝▒žĒÜ│╔ī”╩╣ė├ĪŻ

ĪĪĪĪļSų°Ģr┤·Ą─░lš╣Ż¼Intel░l▓╝┴╦CeleronŽĄ┴ą╠Ä└ĒŲ„ęį╝░ŽÓĻPĄ─ų„░ÕąŠŲ¼ĮMŻ¼ā╚┤µ▀M╚ļ┴╦┴╦SDRAMĢr┤·Ż¼SD(Synchronous Dynamic)RAMę▓ĘQĪ░═¼▓ĮäėæBā╚┤µĪ▒Ż¼Č╝╩Ū168ŠĆĪóĦīÆ64bitĪó3.3VļŖē║Ż¼Ųõ╣żū„įŁ└Ē╩ŪīóRAM┼cCPUęįŽÓ═¼Ą─ĢrńŖŅl┬╩▀Mąą┐žųŲŻ¼╩╣RAM║═CPUĄ─═ŌŅl═¼▓ĮŻ¼ÅžĄū╚ĪŽ¹Ą╚┤²ĢrķgĪŻ

ĪĪĪĪ░ķļSų°Intelį┌═Ų│÷PC100║¾Ż¼ė╔ė┌╝╝ągĄ─░lš╣Ż¼PC100ā╚┤µĄ─800MB/SĦīÆęčĮø▓╗─▄ØMūŃąĶŪ¾Ż¼Č°PC133Ą─ĦīÆ╠ßĖ▀▓ó▓╗┤¾(1064MB/S)Ż¼═¼śė▓╗─▄ØMūŃ╚š║¾Ą─░lš╣ąĶŪ¾ĪŻ┤╦ĢrŻ¼Intel×ķ┴╦▀_ĄĮ¬Üš╝╩ął÷Ą──┐Ą─Ż¼┼cRambus┬ō║Žį┌PC╩ął÷═ŲÅVRambus DRAMĪŻ

ĪĪĪĪRambus DRAM╩ŪRambus╣½╦ŠūŅįń╠ß│÷Ą─ę╗ĘNā╚┤µęÄĖ±ĪŻ╦³▓╔ė├┴╦ę╗ĘN║═SDRAM▓╗═¼Ą─╝▄śŗĪ¬ą┬ę╗┤·Ė▀╦┘║åå╬ā╚┤µ╝▄śŗŻ¼╗∙ė┌ę╗ĘNŅÉRISC(Reduced Instruction Set ComputingŻ¼Š½║åųĖ┴Ņ╝»ėŗ╦ŃÖC)└ĒšōŻ¼▀@éĆ└Ēšō┐╔ęį£p╔┘öĄō■Ą─Å═ļsąįŻ¼╩╣Ą├š¹éĆŽĄĮyąį─▄Ą├ĄĮ╠ßĖ▀ĪŻ

Rambus DRAMĄ─Įė░Ó╚╦Ī¬XDRā╚┤µ╝╝ąg

ĪĪĪĪRambus╩╣ė├400MHzĄ─16╬╗┐éŠĆŻ¼į┌ę╗éĆĢrńŖų▄Ų┌ā╚Ż¼┐╔ęįį┌╔Ž╔²čž║═Ž┬ĮĄčž═¼Ģré„▌ööĄō■Ż¼▀@śė╦³Ą─īŹļH╦┘Č╚Š═×ķ400MHzĪ┴2=800MHzŻ¼└ĒšōĦīÆ×ķ(16╬╗Ī┴2Ī┴400MHz/8)1.6GB/sŻ¼ŽÓ«öė┌PC100Ą─ā╔▒ČĪŻ┴Ē═ŌŻ¼Rambusę▓┐╔ęįā”┤µ9╬╗ūų╣ØŻ¼Ņ~═ŌĄ─ę╗╬╗╩Ūī┘ė┌▒Ż┴¶╬╗Ż¼┐╔─▄ęį║¾Ģ■ū„×ķECC(Error Checking and CorrectionŻ¼Õeš`Öz▓ķą▐š²)ąŻ“×ĪŻ

ĪĪĪĪė╔ė┌RDRAMĄ─╣ż╦ćÅ═ļsŻ¼ārĖ±▀^Ė▀Ż¼Č°ŪęRambus╣½╦Š▀Ćę¬╩š╚ĪŽÓæ¬Ą─░µÖÓ╩š┘MŻ¼į┘╝ė╔Ž¶[Ą├ʹʹōPōPĄ─i820╗ž╩š╩┬╝■ĪŻŲõ╦³ÅS╝ę│÷ė┌╩ął÷┐╝æ]Ż¼Ė∙ō■RambusļpŽ“├}ø_Ą─╠ž³cŻ¼╠ß│÷┴╦DDR SDRAMŻ¼ę▓Š═╩Ū╬ęéā¼Fį┌ūŅų„┴„Ą─ā╚┤µŚlĪŻ

ĪĪĪĪūŅ│§DDRā╚┤µ▓ó╬┤Ą├ĄĮIntelĄ─ų¦│ųŻ¼ų╗ėą╔┘▓┐Ęų╩╣ė├Athlon╠Ä└ĒŲ„Ą─ąŠŲ¼ĮM▓┼ų¦│ųŻ¼Ą½╩ŪļSų°╩ął÷Ą─öU┤¾Ż¼Intelę▓ØuØuĄ─░┤▐Ó▓╗ūĪŻ¼▀@ĘNĮ╣╝▒į┌═■╩óļŖūė═Ų│÷P4X266ąŠŲ¼ĮM║¾ĮKė┌▒¼░lŻ¼═Ų│÷┴╦Intel╩╣ė├DDRā╚┤µĄ─Ą┌ę╗ĘNP4ąŠŲ¼ĮMĪ¬i845DĪŻć└Ė±šfüĒŻ¼ų▒ĄĮ▀@éĆĢr║“Ż¼Intel▀Ćø]ėą═Ļ╚½ÆüŚēų¦│ųRDRAMā╚┤µĄ─i850ąŠŲ¼ĮMĪŻ

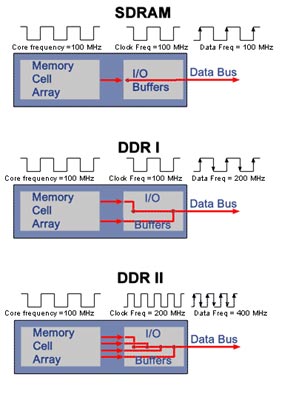

ĪĪĪĪDDR SDRAM(Dual Date Rate SDRAM)║åĘQDDRŻ¼ę▓Š═╩ŪĪ░ļp▒Č╦┘┬╩SDRAMĪ░Ą─ęŌ╦╝ĪŻDDR SDRAMę▓┐╔ęįšf╩Ūé„ĮySDRAMĄ─╔²╝ē░µ▒ŠŻ¼ūŅųžę¬Ą─Ė─ūā╩Ūį┌öĄō■é„▌öĮń├µ╔ŽĪŻ

ĪĪĪĪDDRį┌ĢrńŖą┼╠¢╔Ž╔²čž┼cŽ┬ĮĄčžĖ„é„▌öę╗┤╬öĄō■Ż¼▀@╩╣Ą├DDRĄ─öĄō■é„▌ö╦┘Č╚×ķé„ĮySDRAMĄ─ā╔▒ČĪŻė╔ė┌āHČÓ▓╔ė├┴╦Ž┬ĮĄŠēą┼╠¢Ż¼ę“┤╦▓ó▓╗Ģ■įņ│╔─▄║─į÷╝ėĪŻų┴ė┌Č©ųĘ┼c┐žųŲą┼╠¢ät┼cé„ĮySDRAMŽÓ═¼Ż¼āHį┌ĢrńŖ╔Ž╔²Šēé„▌öĪŻ

ĪĪĪĪ╦³┴Ēę╗éĆ├„’@Ą─Ė─ūāŠ═╩Ūį÷╝ė┴╦ę╗éĆļpŽ“Ą─öĄō■┐žųŲĮė─_ĪŻ«öŽĄĮyųą─│éĆ┐žųŲŲ„░l│÷ę╗éĆīæ╚ļ├³┴ŅĢrŻ¼ę╗éĆDQSą┼╠¢▒ŃĢ■ė╔ā╚┤µ┐žųŲŲ„╦═│÷ų┴ā╚┤µĪŻČ°é„ĮySDRAMĄ─DQSĮė─_ätė├üĒį┌īæ╚ļöĄō■Ģrū÷öĄō■š┌šų═¼▓Įé„▌öŻ¼▓╗Ģ■ėą─│éĆ╚╦öĄō■é„▌ö▌^┐ņŻ¼Č°ėąą®öĄō■é„▌ö▌^┬²Ą─ŪķørĪŻ ļSų°Intelą┬ę╗┤·ąŠŲ¼ĮMĪ¬i915/925Ą─░l▓╝Ż¼╬ęéāėųėŁüĒ┴╦ā╚┤µĄ─ėųę╗éĆĪ░┤║╠ņĪ▒Ż¼DDR IIĪŻ

ĪĪĪĪDDR-IIā╚┤µīó╩Ū¼FėąDDR-Iā╚┤µĄ─ōQ┤·«aŲĘŻ¼╦³éāĄ─╣żū„ĢrńŖŅAėŗīó×ķ400MHz╗“Ė³Ė▀ĪŻÅ─JEDECĮM┐Śš▀ĻU╩÷Ą─DDR-IIś╦£╩üĒ┐┤Ż¼ßśī”PCĄ╚╩ął÷Ą─DDR-IIā╚┤µīóōĒėą400-Īó533Īó667MHzĄ╚▓╗═¼Ą─ĢrńŖŅl┬╩ĪŻ

ĪĪĪĪĖ▀Č╦Ą─DDR-IIā╚┤µīóōĒėą800-Īó1000MHzā╔ĘNŅl┬╩ĪŻDDR-IIā╚┤µīó▓╔ė├200-Īó220-Īó240-ßś─_Ą─FBGAĘŌčbą╬╩ĮĪŻūŅ│§Ą─DDR-IIā╚┤µīó▓╔ė├0.13╬ó├ūĄ─╔·«a╣ż╦ćŻ¼ā╚┤µŅw┴ŻĄ─ļŖē║×ķ1.8VŻ¼╚▌┴┐├▄Č╚×ķ512MBĪŻ

ĪĪĪĪDDR-IIīó▓╔ė├║═DDR-Iā╚┤µę╗śėĄ─ųĖ┴ŅŻ¼Ą½╩Ūą┬╝╝ągīó╩╣DDR-IIā╚┤µōĒėą4ĄĮ8┬Ę├}ø_Ą─īÆČ╚ĪŻDDR-IIīó╚┌╚ļCASĪóOCDĪóODTĄ╚ą┬ąį─▄ųĖś╦║═ųąöÓųĖ┴ŅĪŻDDR-IIś╦£╩▀Ć╠ß╣®┴╦4╬╗Īó8╬╗512MBā╚┤µ1KBĄ─īżųĘįOų├Ż¼ęį╝░16╬╗512MBā╚┤µ2KBĄ─īżųĘįOų├ĪŻDDR-IIā╚┤µś╦£╩▀Ć░³└©┴╦4╬╗ŅA╚ĪöĄ(pre-fetch of 4 bits)ąį─▄Ż¼DDR-I╝╝ągĄ─ŅA╚ĪöĄ╬╗ų╗ėą2╬╗ĪŻ

ĮYšZŻ║

ĪĪĪĪ┐vė^ęį╔ŽĄ─ā╚┤µÜv╩ĘŻ¼╬ęéā┐┤ĄĮÅ─ūŅįńų╗─▄▀_ĄĮ30nsĪó256KBĄ─ā╚┤µŚlĄĮSDRAMę╗Įy╠ņŽ┬Ż¼čė└mĄĮ¼FĮ±ā╚┤µų„┴„DDR IŻ¼Č°¼F╚ńĮ±DDR IIę▓ĖĪ│÷╦«├µŻ¼▀Ćėą╔ą╬┤ēm░Ż┬õČ©Ą─QBMā╚┤µŻ¼Ģr┤·Ą─░lš╣┤┘▀Mų°ėŗ╦ŃÖC╝╝ągĄ─▓╗öÓ▀M▓ĮŻ¼╠Äį┌▀@éĆ╝╝ąg’w╦┘░lš╣Ą──Ļ┤·Ż¼╬┤üĒę▓įS▀ĆėąĖ³ČÓĄ─Š½▓╩ĪŻ